Vivado

Intermitente un programa MicroBlaze

Ahora que he terminado un proyecto de MicroBlaze quiero poder tener el programa Inicie en el arranque. Miré y no podía encontrar cualquier instrucción completa para hacer una carga de programa MicroBlaze en el arranque. En esto utilizaré el Arty como

Agregar IP a Vivado

Vivado es una gran herramienta para el desarrollo de FPGA. Hay algunos casos cuando la IP de no adaptarse a sus necesidades. Por suerte puede añadir custom IP cores en Vivado en unos pocos pasos. Para este Instructable voy a utilizar el repositorio d

Cómo utilizar Vivado Simluation

He realizado este proyecto de simulación de una clase en línea. El proyecto está escrito en Verilog. Se utilizar la simulación en Vivado a visualizar la forma de onda en enable_sr(enable digit) del parada de reloj proyecto creado anteriormente. Ademá

FPGA temporizado remoto (IR)

¿Su compañero de cuarto nunca dejó la TV en tarde en la noche? ¿Si alguna vez queríamos limitar cuánto usted ver televisión? Bien este dispositivo le ayudará a controlar su televisor y asegúrese de que se apaga de manera oportuna.Con su propio tabler

Cómo tu propia máquina de la garra del código

Junto con muchas otras personas, tengo recuerdos de la infancia de caminar en una sala de cine, tienda de comestibles o arcade y ver una caja de cristal llena de juguetes. Siempre fue eso un juguete enterrado o situado justo en la parte superior que

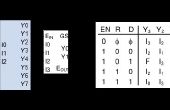

Proyecto 5: Multiplexor, decodificador, codificador y palanca de cambios

En este proyecto se diseño un multiplexor, un decodificador, codificador y una palanca de cambios usando Verilog HDL. En lugar de construir el circuito utilizando los operadores de la lógica, usted aprenderá a describir un circuito su comportamiento

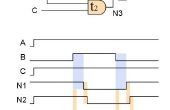

Proyecto 7: Simular falla y demora en circuitos combinacionales

En este proyecto, vamos a examinar el retardo en circuitos combinacionales. Vamos a decirle al simulador de la demora de cada puerta en Verilog y simular los circuitos para ver cómo retardo puede afectar el comportamiento de un circuito combinacional

Cómo utilizar Verilog y 3 Basys para hacer contador binario de 3 bits

He realizado este proyecto para una clase en línea. El proyecto está escrito en Verilog. Los módulos de divisor y contador del reloj fueron proporcionados. Mi tarea fue escribir el módulo superior para mostrar la salida de 3 bits del contador en el d

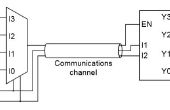

Proyecto 6: Un sistema de comunicación Simple

En este proyecto, se diseño un mux 4 a 1 y un decodificador con una señal de enable como un "mux de" implementar un transmisor de datos en serie simple. Mux y de mux se implementará en dos ficheros Verilog para su reutilización futura. Otro fich

Proyecto 1.2: Utilizar modificadores a los LEDs de Control

Este proyecto muestra cómo utilizar Verilog HDL con una tarjeta FPGA. En este proyecto utilizará un interruptor en su tabla FPGA para encender un LED. Al hacer esto, aprenderás los primeros pasos de escritura de código de Verilog y observar cómo un i

Automático cerrado ratón inalámbrico (prototipo)

Descargo de responsabilidad: Este es un prototipo y hará que su ratón inalámbrico "con cable". Además, dependiendo de su ratón, puede perder su capacidad de deslizar a través de la mesa/alfombrilla de ratón.Para nuestro proyecto final en CPE 133

FPGA Digilent proyectos con Scripts Tcl

Proyectos FPGA en VHDL o Verilog fácilmente pueden ser adaptados para funcionar en Vivado usando scripts tcl (cosquillas!). Mientras que la mayoría de usuarios está familiarizada con el método de interfaz (GUI) de usuario gráfica estándar de trabajo

Cómo convertir de UCF a archivo XDC

Con el lanzamiento de Xilinx Vivado hace un tiempo, muchas personas están buscando diseños de referencia, pero encontrando sólo para su uso con ISE. Por suerte siempre y cuando no hay ninguna IP, transferencia de un diseño es bastante sencillo. Todo

Proyecto 1.1: Introducción a la ingeniería Digital y tableros FPGA

Esta es la primera de una serie de proyectos utilizando materiales de Digilent que se crean para EE214 en la Universidad Estatal de Washington. Sin embargo, decidimos que queríamos hacerlos más accesibles al general pública, por lo que les estoy crea

Proyecto 3.1: Mayoría de 5

¿Cómo se podría encontrar una mayoría de los votos si cada uno de los cinco votantes tiene un interruptor para votar sí o no? La lógica es bastante simple y se utilizará en este proyecto. Cualquier momento hay tres o más de los cinco que voto Sí, ent

Primeros pasos con Arty

Acaba de lanzar una nueva placa de desarrollo FPGA Digilent. El consejo artístico. El Arty es diseñado para ser usado exclusivamente con Xilinx Vivadoy diseñado específicamente para uso con microblaze.Este tutorial cubre cómo utilizar fuera de diseño

Para comenzar con MicroBlaze por el Arty

Arty es una placa de desarrollo FPGA versátil que es capaz de ejecutar el procesador softcore MicroBlaze. Este núcleo IP permite la programación de la FPGA con el SDK de Xilinx.Se supone que se ha seguido el siguiente tutorial para instalar los archi

Cómo usar un Joystick con una FPGA

Este instructable es otra parada en mi viaje para construir el juego garra impulsado por una FPGA. Anteriormente escribí cómo controlar un motor paso a paso con una FPGA. Ahora necesitaba para el control de un joystick por lo que finalmente me puedo

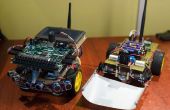

FPGA-accionado la búsqueda autónoma y rescate de vehículos

UPDATE2: revise http://www.digilentdesigncontest.com/2015-eu-contest-entries.html para el código fuente completo y la documentación.UPDATE1: añadido un nuevo módulo - 3 ejes magnetómetro (brújula digital). Consulte el paso 2 para más detalles.Este pr

Consiguiendo comenzado con Xilinx Vivado con Digilent SDMONexys 4 FPGA 1 - construir múltiples entradas y lógica puerta

Hago este instructable porque parece que no es sencillo empezar tutorial para enseñar a la gente a utilizar la última herramienta de Xilinx Vivado CAD. Por lo tanto, quiero usar el simple que múltiples entradas de puerta de diseño a pie a través de X