FPGA

Intermitente un programa MicroBlaze

Ahora que he terminado un proyecto de MicroBlaze quiero poder tener el programa Inicie en el arranque. Miré y no podía encontrar cualquier instrucción completa para hacer una carga de programa MicroBlaze en el arranque. En esto utilizaré el Arty como

El curso intensivo de ingeniería (responsables)

En el verano de 2015, formalmente me introdujo al mundo de la ingeniería eléctrica la oportunidad de hacer una pasantía para una pequeña empresa de ingeniería, Digilent Inc. Como una de las únicas personas en mi grupo de amigo con un fondo de educaci

Breakout juego

Esta es una de mi proyecto para el curso de diseño de circuitos integrados. El kit utilizado para desarrollar es FPGA SPARTAN 3E y nuestro programa está codificado con el uso de diseño de XILINX ISE.La estructura básica del juego es fácil de entender

Huracán

Huracán es un emocionante remake del clásico juego arcade ciclón. En este juego hemos puesto 16 LEDs alrededor de un círculo con el LED más cercano a usted ser un diverso color que el resto. El objetivo principal de este juego es acumular tantos bole

Añadir LEDs al juego garra

El juego de garra es muy bueno pero siempre hay una manera de mejorar un proyecto. Para mejorar el juego garra tiras de LED van a añadirse a la base debido a que ningún proyecto es completa sin un número excesivo de LEDs.Lamentablemente el proyecto p

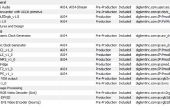

Agregar IP a Vivado

Vivado es una gran herramienta para el desarrollo de FPGA. Hay algunos casos cuando la IP de no adaptarse a sus necesidades. Por suerte puede añadir custom IP cores en Vivado en unos pocos pasos. Para este Instructable voy a utilizar el repositorio d

Cómo utilizar Vivado Simluation

He realizado este proyecto de simulación de una clase en línea. El proyecto está escrito en Verilog. Se utilizar la simulación en Vivado a visualizar la forma de onda en enable_sr(enable digit) del parada de reloj proyecto creado anteriormente. Ademá

Optimizador de paneles solares FPGA

Fotovoltaica: Radiación máxima detecciónLas células fotovoltaicas convierten la luz en electricidad con silicona u otro material semiconductor mediante la absorción de fotones con energía suficiente golpear electrones libres por lo que puede fluir co

FPGA LED FSM

Resumen:Los ingenieros de diseño: Ryan Ortiz, Chris Harlow, Dalton Wunderlich y Ramón CrespoEste proyecto fue completado como parte de una clase de CPE 133 como proyecto final.Esta FPGA está conectado a un sensor de movimiento infrarrojo, así como un

Imagen de FPGA a VGA

Para algunos estudiantes de electrónica una FPGA de metal desnuda puede ser bastante aburrida, sabiendo que un microcontrolador puede hacer un mucho mejor trabajo en mucho la situación. Sin embargo, eso no significa que la FPGA es aburrido sí mismo!

Interfaz el controlador AXI TFT con la IP de MIG y usarlo a pantalla utilizando el puerto VGA en la placa DDR Nexys4

Este tutorial es la tercera parte de una serie de tres partes que se ocupa de configurar la IP MIG proporcionado por Xilinx para utilizar la memoria DDR a bordo de la Junta de Nexys4 y la interfaz con la IP de TFT AXI para utilizar el puerto VGA en l

Configurar la IP de la serie MIG 7 para usar la memoria DDR en placa de 4 SDMONexys de Digilent

Este tutorial es la segunda parte de una serie de tres partes que se ocupa de establecer la IP MIG proporcionado por Xilinx para usar la memoria DDR a bordo de la Junta de Nexys4 y la interfaz con la IP de TFT de AXI que utilizan el puerto VGA en la

El proyecto RoseAce

dirás: pero mostrar otro punto de vista.Y estaban bien, pero esta la primera de ellas para incrustar un embedidos (que es una pequeña computadora) en su hoja: gracias a que somos capaces de conectarse vía wifi a la hoja (sí todavía se recibe la señal

IPSec usando OpenSwan Zybo

OPENSWAN es una implementación de IPsec para Linux. Tiene soporte para la mayoría de las extensiones (RFC + IETF borradores) relacionados con IPsec, incluyendo IKEv2, certificados digitales X.509, NAT Traversal y muchos otros.Antes de comenzar este t

Proyecto 2.1: Implementar un circuito de lógica Simple

En este proyecto, se descargar un archivo de bits a la placa para configurar la FPGA con cuatro diferentes circuitos de lógica. Los circuitos utilizan botones e interruptores para las entradas y LEDs para las salidas. Debe sondear los circuitos lógic

Código Morse entrada-salida

este proyecto sirve como un proyecto final para el 2220 de ECE en la Universidad de Manitoba. El propósito de la el proyecto debe resolver un problema práctico con nuestro conocimiento de la FPGA proporcionado. El problema que intenta resolver es con

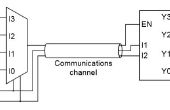

Proyecto 6: Un sistema de comunicación Simple

En este proyecto, se diseño un mux 4 a 1 y un decodificador con una señal de enable como un "mux de" implementar un transmisor de datos en serie simple. Mux y de mux se implementará en dos ficheros Verilog para su reutilización futura. Otro fich

Tableta de FPGA de4

The DE4 Tablet es una tableta portátil diseñado por el laboratorio de computación de la Universidad de Cambridge.Utiliza una tarjeta Terasic DE4 FPGA con un FPGA de Altera Stratix IV. Cuenta con un conjunto completo de periféricos de la DE4, así com

CPLD de altera Max II Blink Led

Hoja de datos-Materiales:-Leds-CablesLED 1, código de verilog es:módulo ledblink(clk,led);entrada clk; salida de led; REG conducido;cnt de reg [23:0];siempre clk) comenzar cnt < = cnt + 1' b1; LED < = cnt [23];finalendmoduleSi usted necesita más inf

FPGA LED Auto Dimmer

Esta guía le permitirá construir un atenuador temporizado con sólo una FPGA y un tiempo. Temporizador del atenuador restablecerá solamente si se cambian los ajustes de tiempo o si se pulsa el botón de reset. Más sobre este tema en los siguientes paso